Introduction

On May 23, the Taiwan Semiconductor Manufacturing Company (TSMC) will hold its annual Technology Forum in Hsinchu. This year, the forum promises to showcase TSMC’s latest advancements, with a significant focus on the groundbreaking 3nm FinFLEX technology.

Industry insiders are eagerly anticipating the event, especially given TSMC’s crucial role in the development of Apple’s M4 chip, which has already made waves in the tech world.

Follow us on Linkedin for everything around Semiconductors & AI

FinFLEX: The Secret Weapon Behind Apple’s M4 Chip

TSMC’s 3nm FinFLEX technology is hailed as the driving force behind Apple’s powerful M4 chip.

The M4 chip is a testament to TSMC’s leadership in advanced semiconductor processes. Compared to previous 3nm technologies, the N3E process, which is part of TSMC’s 3nm family, simplifies manufacturing steps and relaxes some parameters to improve yield and productivity.

Although the transistor density of N3E is not significantly higher than N3B, the integration of FinFLEX technology enhances the performance and power efficiency of the M4 chip.

High Foreign Investment and Market Impact

Foreign investors have shown strong confidence in TSMC, purchasing 408,700 TSMC contracts this year, with a market value exceeding 21 trillion yuan.

This investment represents over 32% of Taiwan’s stock market value. With a price-to-earnings ratio of 21.7 times, TSMC is positioned as a key player among AI technology leaders.

Read More: GPT-4o: 12 Mind-Blowing Use Cases That Change How We Interact with AI – techovedas

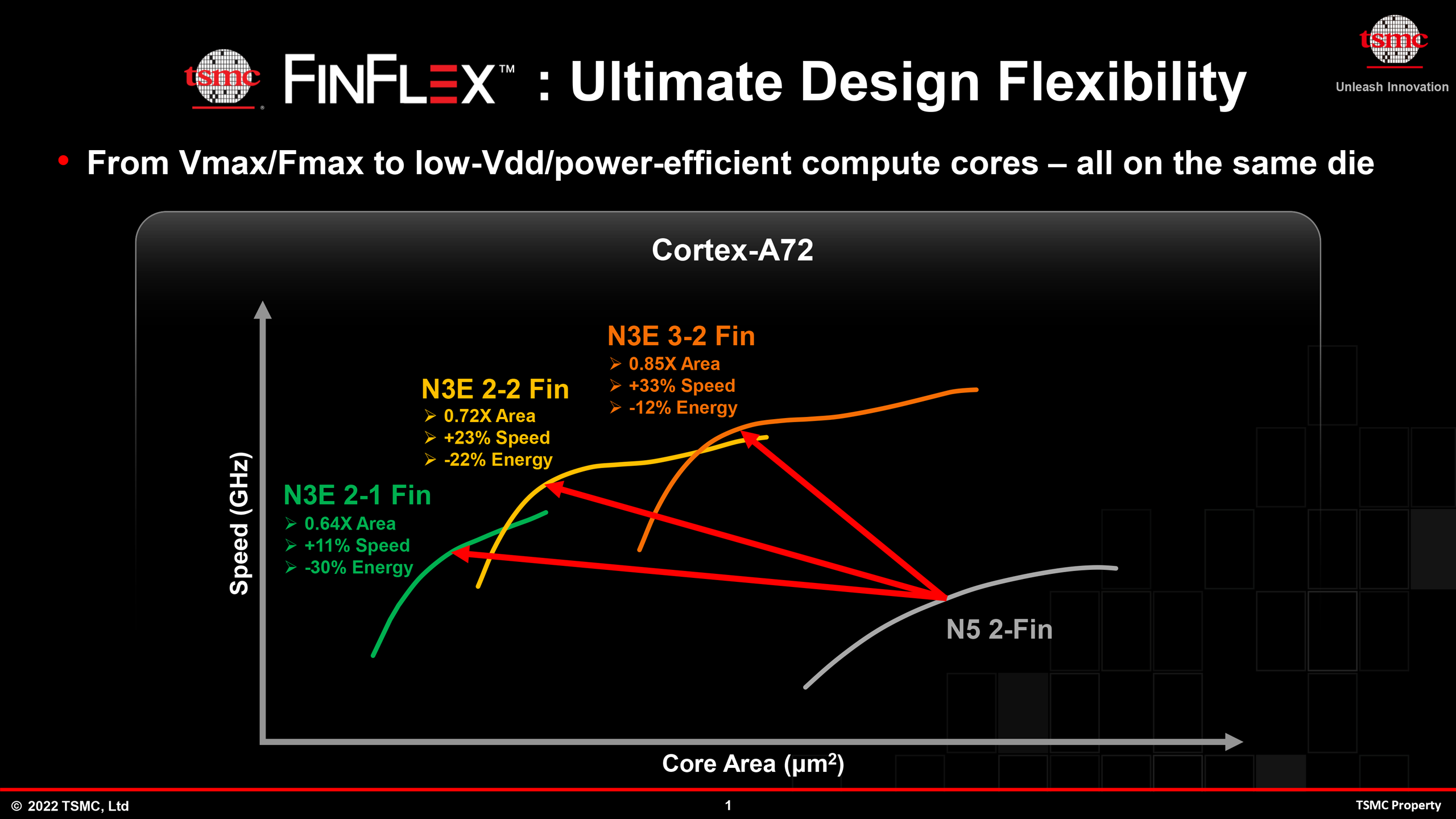

Advanced Packaging and Customization with FinFLEX

FinFLEX technology allows chip designers to mix and match different types of standard cells within a single module.

This flexibility enables the optimization of performance, power consumption, and area (PPA) configurations according to specific customer requirements. This capability is particularly beneficial for applications needing a high number of core CPUs and GPUs.

At the forum, TSMC is also expected to introduce its next-generation NanoFlex technology.

This innovation allows the adjustment of standard component heights to meet customized performance, power consumption, and area requirements.

With NanoFlex, TSMC aims to maintain its competitive edge in the upcoming 2nm market.

Read More: 20 Times Faster than 5G: Japan Unveils World’s First High-Speed 6G Device – techovedas

Leading the Industry with 2nm Technology

TSMC continues to lead the industry with its 2nm process technology, addressing the growing demand for energy-efficient computing.

The company has announced that almost all major AI innovators are collaborating with TSMC, underscoring its pivotal role in the tech ecosystem.

Read More: Why Smartphone SoCs need a Dedicated AI Processors (For eg. NPUs)? – techovedas

Comparative Insights: N3E vs. N5 and N3B

According to TSMC’s public data, the N3E process offers similar performance levels to the 5nm process at the SRAM level, with higher logic circuit density compared to N3B. However, the N3E’s scale is approximately 0.94 times that of the N5, while the N3B scale is around 0.88 times.

| Feature | N3E | N5 | N3B |

|---|---|---|---|

| Transistor Size | 3nm | 5nm | 3nm |

| Logic Density | Higher | Lower | Lower |

| SRAM Performance | Comparable to N5 | – | – |

| Scale Factor (compared to N5) | Approximately 0.94x | 1x | Approximately 0.88x |

| Application | Next-gen processors, high-performance computing | High-performance computing, mobile devices | High-performance computing, mobile devices |

| Notable Features | Enhanced performance and power efficiency with FinFLEX technology | Advanced performance with improved power efficiency | Improved yield and productivity, simplification of process parameters |

Read More:AI on Steroids: Microsoft Unveils Copilot+ PCs with Built-in Generative AI Capabilities – techovedas

Future Roadmap: N3P, N3X, and Beyond

Looking ahead, TSMC plans to expand its 3nm family with the introduction of N3P and N3X processes.

These processes aim to further enhance performance at the 3nm node. Additionally, TSMC’s NanoFlex technology, which follows the Nanosheet, will likely be a highlight of the technical forum.

NanoFlex optimizes the combination of high and low components within the same design block, achieving the best balance of power consumption, performance, and area for various applications.

Read More: Intel’s Lunar Lake Processors Set to Revolutionize AI PC Market in Q3 2024 – techovedas

Conclusion

TSMC’s Technology Forum on May 23 is set to be a landmark event, showcasing the company’s innovations in semiconductor technology.

With the introduction of FinFLEX and NanoFlex technologies, TSMC continues to push the boundaries of what’s possible in chip design and manufacturing, solidifying its position as a leader in the semiconductor industry.