Introduction

Intel has unveiled its latest architectural innovation with Lion Cove, a significant evolution in its P-Core lineage. Lion Cove refers to Intel’s latest CPU architecture designed for their upcoming Lunar Lake processors. It signifies a major leap in CPU design with a focus on improved performance and efficiency.

Tracing its roots back to the P6 architecture found in the Pentium Pro, Intel’s P-Cores have undergone numerous transformations through iterations like the Pentium III, Sandy Bridge, and Golden Cove. The Lion Cove architecture represents a major departure from previous designs, introducing several groundbreaking changes that promise to redefine CPU performance and efficiency.

Intel’s Lion Cove architecture is indeed a significant advancement in CPU design, slated for their upcoming Lunar Lake processors.

Here’s a breakdown of its key features:

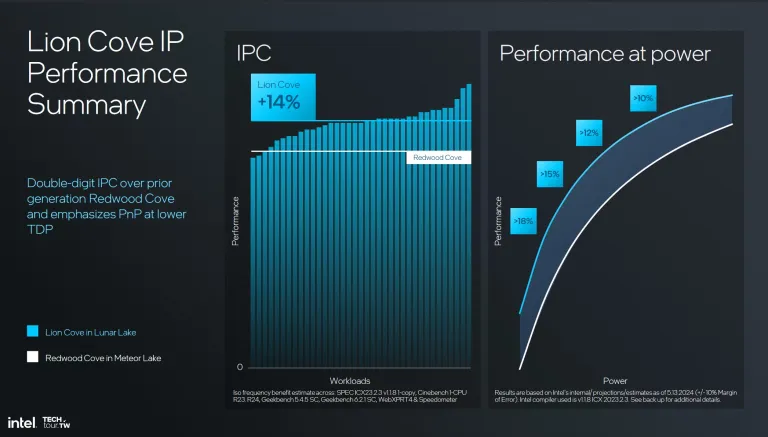

- Performance Boost: Lion Cove boasts a predicted double-digit increase in instructions per clock (IPC) over its predecessor, Redwood Cove. This translates to faster processing of instructions for improved overall performance.

- Enhanced Efficiency: The design prioritizes efficiency alongside performance. Improvements like a split math scheduler and a wider core execution engine aim to deliver better performance per watt and better performance per area.

- Multi-Tier Cache Hierarchy: A major revamp of the cache system introduces a new 3-level cache structure. This includes a small, super-fast L0 cache (48KB) for frequently accessed data, a larger L1 cache (192KB) with moderate latency, and a significantly bigger L2 cache (up to 3MB) for handling larger datasets. This tiered approach ensures quicker access to critical data, minimizing latency issues.

- AI-powered Management: Static thermal guard-bands are replaced with AI self-tuning controllers for power management. This allows for more dynamic and efficient power allocation based on real-time workload demands.

Overall, Lion Cove represents a substantial leap in CPU architecture, promising not only substantial performance gains but also improved efficiency and power management. It’s definitely an architecture to watch out for in future Intel processors.

Follow us on Twitter: https://x.com/TechoVedas

Lion Cove architecture

The Lion Cove architecture is pivotal for Intel. It introduces innovations enhancing performance and efficiency. These changes showcase Intel’s commitment to pushing CPU design boundaries.

The architecture ensures Intel’s processors stay at the industry forefront. This article explores Lion Cove’s key features and improvements. It highlights its potential impact on future computing.

Splitting the Scheduler

Traditionally, Intel CPUs used a single unified scheduler. Lion Cove introduces a hexa-ported integer scheduler and a quad-ported vector scheduler.

This separation offers improved power efficiency and simplified core design. Splitting the scheduler allows Intel to effectively clock gate its sections.

If no vector code runs, the vector scheduler can gate the clock, reducing power consumption or reallocating power to other core parts. This potential enables those parts to clock higher.

Enhanced Cache Hierarchy

Lion Cove brings substantial changes to the cache hierarchy, including the addition of a new intermediate cache:

- L0 Cache: Previously known as the L1 cache in prior Cove cores, the L0 cache retains the increased size seen in later Cove cores but reduces latency to 4 cycles, akin to Skylake.

- L1 Cache: Introducing a new intermediate cache, the L1 offers 192KB of storage with a 9-cycle latency. This cache acts as a buffer between the faster L0 and the larger L2 cache.

- L2 Cache: The L2 cache size has increased to 3MB, with a slight latency increase to 17 cycles. Despite the larger size and the additional cache level, the L2 maintains efficient performance. Both the L0 and L1 caches can process up to 128B per cycle, while the L2 cache bandwidth limits to 64B per cycle for power and area savings.

Read More: Top 5 Jobs in AI(Artificial Intelligence) in 2024 – techovedas

Hyperthreading Optional

The Lion Cove architecture introduces optional Hyperthreading, tailored to specific products. For instance, in Lunar Lake, Intel disabled Hyperthreading and removed its supporting components, reducing die size and simplifying Thread Director’s tasks.. This change allows Thread Director to focus only on P-Cores and E-Cores, reducing complexity. However, this design choice may not apply to all Lion Cove implementations, allowing for potential Hyperthreading support in products like Arrow Lake or future server CPUs.

Read More: $445 Million in Damages: Jury Slaps Micron in Patent Trial Against Netlist – techovedas

Other Improvements

Lion Cove features several enhancements across different areas:

- Front-End Enhancements: The fetch rate has increased to 48 bytes per cycle, the Uop cache size has been expanded, and branch prediction has been improved to feed the widened back-end.

- Widened Core: The core width has increased from 6 to 8, with the reorder buffer size expanded from 512 to 576 entries. While Intel has not specified if the register files have increased in size, associated structures with the reorder buffer have been scaled accordingly.

- Integer Execution Units: The number of ALUs has increased to 6, and the integer multiply units have tripled to 3, addressing workloads that require additional integer multiply capability.

- Vector Execution Units: The number of SIMD ALUs has increased to 4, and a second floating-point divider has been added, enhancing the throughput and latency of division operations.

- Memory Subsystem: The L1 DTLB capacity has increased to 128 entries, and a third store addressing AGU has been added.

Follow us on Linkedin for everything around Semiconductors & AI

Conclusion

With these changes, Lion Cove boosts performance per clock by 14%, a significant improvement.The architecture’s shift towards a more customizable design enables Intel to better optimize P-Cores for specific

applications.

This customization spans from consumer PCs to high-performance servers. It allows Intel to tailor the performance and features of P-Cores to meet diverse computing needs.

This flexibility ensures that Intel’s processors remain competitive across a wide range of use cases. This innovation positions Intel to meet diverse computing needs, ensuring its processors remain at the cutting edge of technology.

Intel’s Lion Cove architecture signifies a new era in CPU design, combining enhanced performance with greater flexibility. These advancements underscore Intel’s dedication to innovation and its commitment to delivering top-tier computing solutions.

If you appreciate our articles and journalism, consider supporting us via Patreon or PayPal. Join our Discord to discuss with the Chips and Cheese team and the people behind the scenes.