Introduction

The JEDEC Solid State Technology Association, a leading organization in microelectronics standards development, has announced a significant update to its JEP30 Part Model Guidelines for chiplet. This update, achieved through a groundbreaking collaboration with the Open Compute Project Foundation (OCP), aims to revolutionize chiplet integration within the electronics industry.

Background of JEDEC Chiplet Standardization:

JEDEC and OCP have joined forces to improve chiplet integration through the new JEP30 Guidelines. This collaboration aims to revolutionize chiplet design, manufacturing, and assembly. Here’s a breakdown of the key points:

JEDEC JEP30 PartModel Guidelines: JEDEC established these guidelines to create standardized descriptions of chiplet parts. This allows chiplet builders to electronically share crucial information with customers.

OCP Chiplet Data Extensible Markup Language (CDXML): OCP’s CDXML contributes its open-standard capabilities to JEP30. This integration empowers a unified platform for chiplet and electronic part integration.

Benefits:

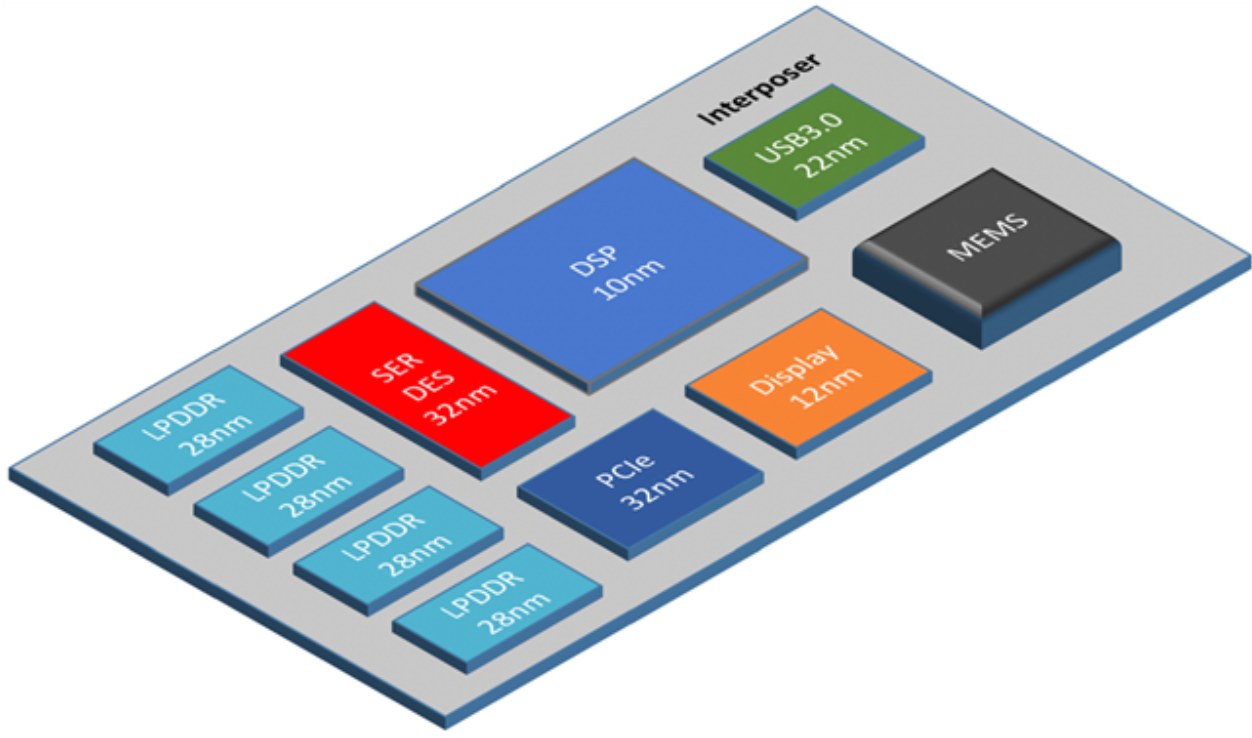

Automation: The standardized format enables automation in System in Package (SiP) design and assembly using chiplets.

Chiplet Descriptions: Chiplet builders can provide information on thermal properties, physical requirements, behavior specifications, and security parameters.

Future-Proofing: The latest release allows for Die-Arrays and supports hierarchical nested arrays, making it scalable for future advancements.

Overall, this collaboration streamlines chiplet integration by offering a standardized language for chiplet descriptions. This paves the way for automation, reduces errors, and fosters innovation in chiplet technology.

Follow us on Linkedin for everything around Semiconductors & AI

What are JEP30 Guidelines?

JEP30 establishes a standardized format for sharing digital part data between manufacturers and end users.

This standardized format works with various CAD tools. It helps in efficient communication and use of part models.

It is useful throughout the product lifecycle, from design to supply chain management.

Read More:Singapore Invests Close to S$300 Million in National Quantum Strategy – techovedas

Key Features of the JEP30 Guidelines

The JEP30 guidelines offer a standardized format compatible with various CAD tools, streamlining communication and utilization of part models. Key features include:

Thermal Properties: Detailed thermal characteristics for efficient thermal management.

Physical and Mechanical Requirements: Specifications ensuring compatibility and reliability in various applications.

Behavior Specifications: Comprehensive descriptions of chiplet behavior for accurate integration.

Power and Signal Integrity Properties: Data on power consumption and signal integrity to ensure optimal performance.

Testing and Security Parameters: Guidelines for in-package testing and security features to safeguard chiplets.

Read More: Huawei Surpasses Samsung to Become Top Foldable Smartphone Maker in Q1 2024 – techovedas

Benefits of the JEP30 Update:

Standardized Chiplet Descriptions: Chiplet builders can now provide standardized digital part descriptions to their customers electronically. This crucial information includes thermal properties, physical and mechanical requirements, behavior specifications, power and signal integrity properties, and testing, in-package, and security parameters.

Automating SiP Design and Assembly: The standardized chiplet descriptions pave the way for automating System in Package (SiP) design and assembly using chiplets. This automation significantly improves efficiency and reduces the risk of human error.

Scalability for the Future: JEDEC and OCP have further extended their collaboration by enabling the PartModel to represent Die-Arrays. This scalability ensures the JEP30 standard can support the evolving needs of the industry for years to come.

Industry Impact:

Mian Quddus, JEDEC Board of Directors Chairman, emphasized the transformative potential of the JEP30 evolution, stating, “Enabling component manufacturers to create standardized digital part models streamlines design processes while reducing human error, marking a transformative leap forward.”

Dr. Cliff Grossner, Chief Innovation Officer at OCP, echoed this sentiment, highlighting the collaboration’s role in building a new silicon supply chain for a commercially viable Chiplet marketplace. He noted, “The addition of a standard representation for Die-Arrays is just one of the follow-on joint work efforts between the OCP and JEDEC communities. We look forward to a long line of follow-on additions to support advanced SiP packaging.”

Looking Ahead:

The big deal about JEDEC and OCP collaborating on chiplet integration with new JEP30 Guidelines boils down to two main benefits: reduced errors and saved time. Here’s why this is a significant advancement:

Chiplets are the future: Chiplet technology allows for building complex processors by combining smaller, specialized chips. This offers advantages like performance gains and lower costs. However, integrating these chiplets efficiently has been a challenge.

Standardization is key: The new JEP30 Guidelines provide a common language for describing chiplets. This means:

- Clear communication: Chiplet designers can accurately convey crucial information like thermal properties, physical requirements, and how the chiplet behaves electronically.

- Reduced errors: Misunderstandings during integration are minimized because everyone’s on the same page.

- Automation potential: With standardized data, designing and assembling systems using chiplets (SiP) becomes more automatable, further reducing errors and saving time.

- Innovation boost: By streamlining the chiplet integration process, JEDEC and OCP are paving the way for faster innovation in chiplet technology. This can lead to more powerful, efficient, and cost-effective chips in the future.

In essence, this collaboration is like creating a universal instruction manual for Legos. It ensures all the pieces (chipsets) fit together smoothly, reducing errors and speeding up the building process (chip design and assembly). This paves the way for more complex and innovative chip designs.

Follow us on Twitter: https://x.com/TechoVedas

Conclusion:

The JEDEC and OCP collaboration on the JEP30 update is a game-changer for the chiplet industry.

By providing standardized chiplet descriptions and enabling automation, this collaboration promises to significantly accelerate chiplet integration, leading to faster development cycles, reduced costs, and improved product quality.

As the industry continues to embrace chiplet technology, the JEP30 guidelines will play a critical role in ensuring its seamless integration and widespread adoption.