Introduction:

In the ever-evolving landscape of semiconductor design, staying ahead of the curve requires innovative solutions that can keep pace with the increasing complexity and demands of modern chips. Cadence, a leader in electronic design automation (EDA), has once again raised the bar with its latest design tool offerings unveiled at the Cadence Live event in Santa Clara.

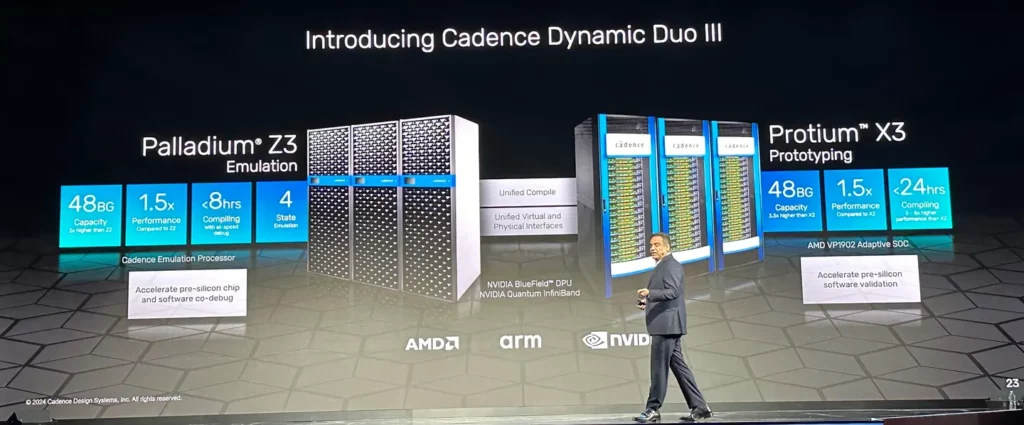

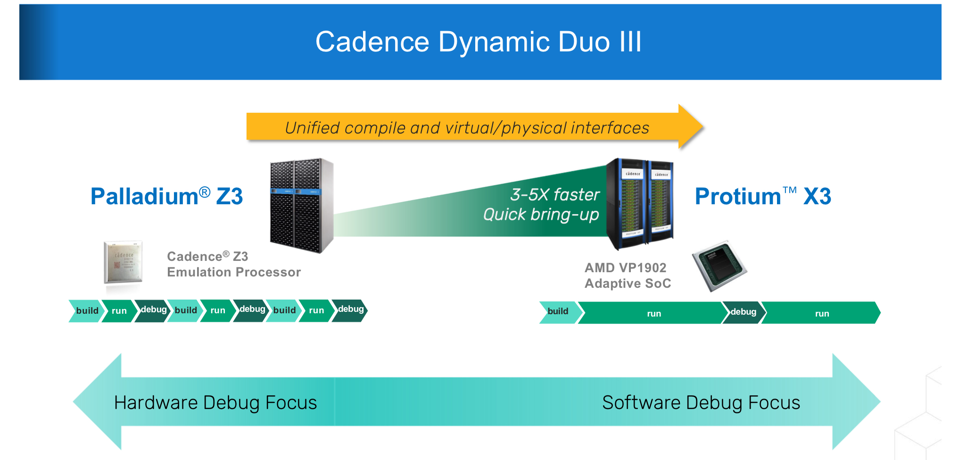

Among the highlights are the next-generation Palladium Z3 and Protium X3 platforms, forming the formidable “Dynamic Duo III,” poised to revolutionize hardware verification and software validation in chip design.

The “Dynamic Duo III” offers a cohesive compilation and virtual/physical interface, enabling designers to expedite the setup of their designs by 3-5 times compared to previous platforms.

Follow us on Linkedin for everything around Semiconductors & AI

Meeting the Challenges of Chip Design:

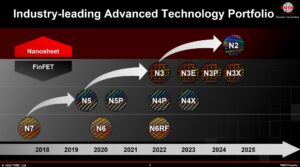

As chip designs continue to grow in complexity, with the emergence of chiplets and the integration of advanced technologies like AI, the challenges faced by design teams have escalated. The need for software and emulation hardware capable of handling the burgeoning transistor counts and intricate architectures is more pressing than ever.

Complexity: As chip designs get larger with billions of transistors, managing the intricate connections and functionalities becomes incredibly challenging.

Time constraints: Traditional design tools might struggle to handle these complex designs. This leads to lengthy design cycles that can delay product launches.

Capacity limitations: Existing software might not have the capacity to handle the sheer amount of data involved in these massive designs.

Cadence’s response to these challenges comes in the form of the Palladium Z3 and Protium X3 systems. These systems offer unparalleled capacity and performance to support chips of up to 48 billion gates.

Read More: What is CMOS 2.0 Revolution: A Paradigm Shift in Chip Design

The Power of the Dynamic Duo:

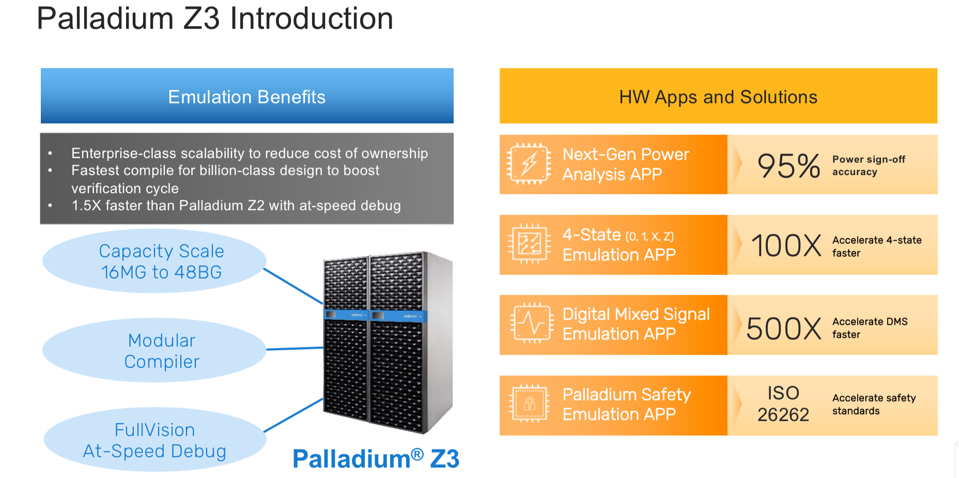

The Palladium Z3 system, with custom Cadence processors, validates chip designs’ logic implementation without breaking them into smaller blocks. Its high capacity ensures seamless verification of intricate designs.

The Protium X3 platform, using AMD FPGAs, specializes in testing software on validated designs, essential for iterative development. The new Palladium Z3 system, with custom Cadence processors, efficiently manages chip designs, supporting up to 48 billion gates without segmentation.

Meanwhile, the Protium X3 platform employs AMD Field Programmable Gate Arrays (FPGAs) to emulate the hardware design, allowing for software testing on designs validated by the Palladium.

Read more: Most Powerful Chips for business PCs: AMD Ryzen Pro CPUs Break the Mold

What is the role of these tools in Chip Design?

Palladium Z3 System:

Purpose: The Palladium Z3 system is primarily designed for validating the logic implementation of chip designs.

Validation of Logic Implementation: Chip designs consist of numerous logic gates arranged in complex architectures. The Palladium Z3 system utilizes custom Cadence processors to simulate and validate the behavior of these logic gates. It ensures that the logic implemented in the design functions correctly according to the intended specifications.

Elimination of Block Breakdown: Traditionally, when dealing with large chip designs, engineers may need to break down the design into smaller blocks for verification due to hardware limitations. However, with its massive capacity, the Palladium Z3 system eliminates the need for such block breakdowns. It can handle designs of up to 48 billion gates seamlessly, allowing for comprehensive validation without compromising on accuracy.

Seamless Verification: The Palladium Z3 system’s high capacity allows engineers to verify intricate designs seamlessly. This ensures thorough testing of all aspects of the chip’s logic before advancing to the next stage of development.

The Palladium Z3 system aids in hardware debugging, while the FPGA-driven Protium X3 platform emulates the hardware design to facilitate software debugging.

Protium X3 Platform:

Purpose: The Protium X3 platform serves as a crucial component in the iterative development process by specializing in software testing on validated designs.

Software Testing: Once the logic implementation of the chip design is validated using the Palladium Z3 system, the next step is to test the software that will run on the finalized hardware design. The Protium X3 platform, powered by AMD Field Programmable Gate Arrays (FPGAs), facilitates this software testing phase.

Iterative Development Link: The Protium X3 platform acts as a bridge between hardware validation and software development. It allows engineers to test and debug software in a hardware environment that closely resembles the final chip design. This iterative approach ensures that any issues or bugs in the software are identified and addressed early in the development cycle.

Critical Link in Development Process: The Protium X3 platform is crucial for software testing on validated designs. It verifies software compatibility and functionality with the hardware design. This ensures the production of high-quality chips.

The Palladium Z3 system validates chip design logic without block breakdowns. The Protium X3 platform specializes in software testing on validated designs. Together, they accelerate chip design verification and validation, ensuring faster time-to-market and improved product reliability.

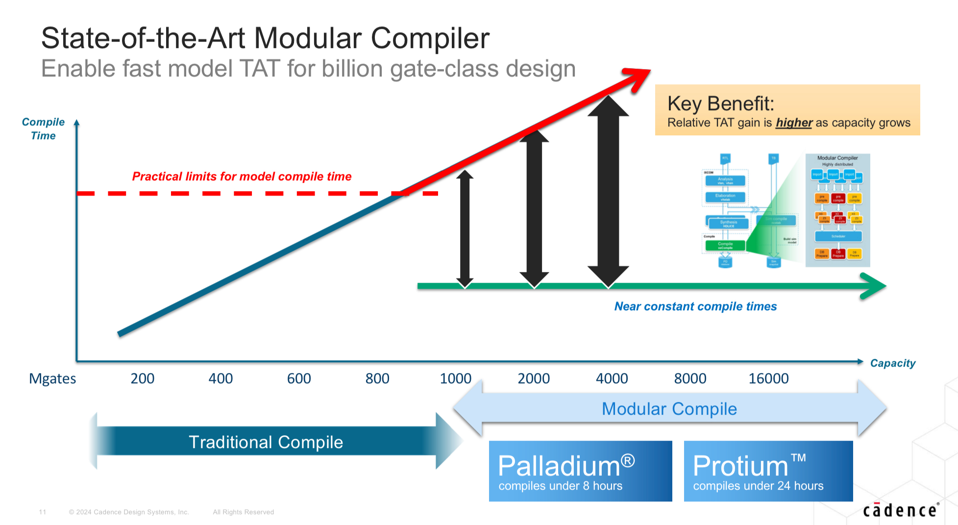

For chip designs reaching into the billion-gate scale, Cadence compilers ensure compile times remain nearly constant

Accelerating Innovation with Domain-Specific Apps:

Cadence’s commitment to innovation extends beyond hardware, as evidenced by the introduction of domain-specific apps for the Palladium Z3 system.

The Palladium Z3 system has expanded its capabilities to include domain-specific applications. This provides users with a comprehensive suite for effectively managing the complexity of system and semiconductor design.

These applications encompass a 4-State Emulation App, Real Number Modeling App, and Dynamic Power Analysis App. Notably, the 4-State emulation app can enhance emulation speeds by up to 100-fold. The Digital Mixed Signal emulation app offers a remarkable 500-fold acceleration in speed.

Notably, the 4-State Emulation App can deliver a staggering 100-fold acceleration in emulation speed, enhancing verification accuracy and throughput.

In addition to its hardware offerings, Cadence provides support for various applications that greatly enhance design productivity.

Read More: 7 Job Profiles in Semiconductor Chip Design

Cadence new design tool: Industry Recognition and Collaboration

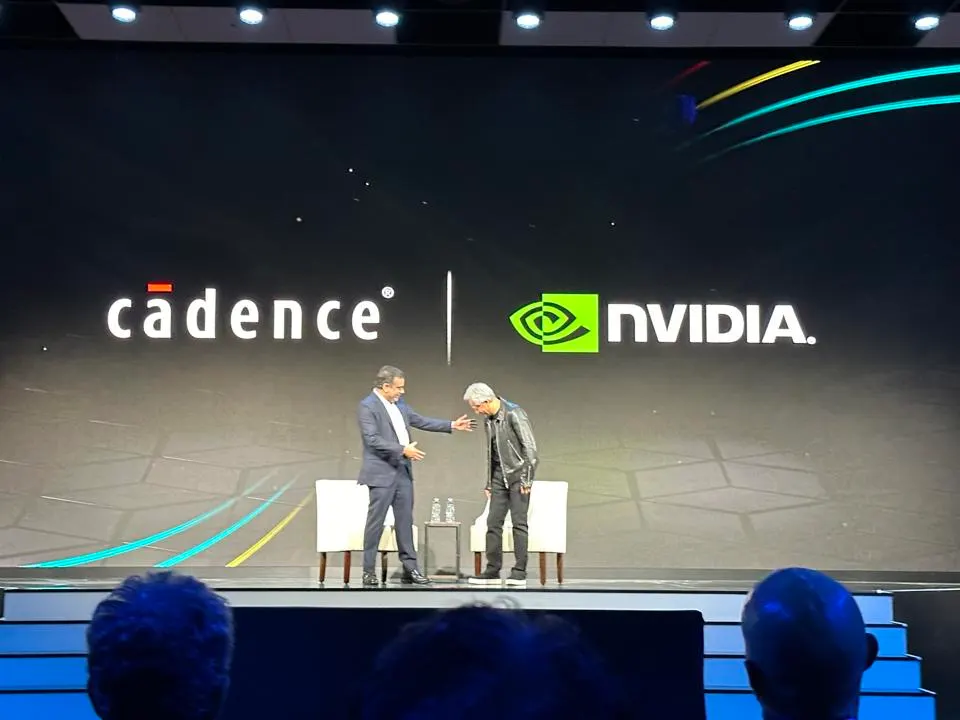

The significance of Cadence’s advancements is underscored by the endorsement of industry giants like Nvidia and Arm. Jensen Huang, CEO of Nvidia, lauded Cadence’s Palladium system, highlighting its indispensable role in enabling groundbreaking projects like Blackwell.

“Nvidia has the largest installation of Palladium systems in the world. Blackwell would have been impossible without Cadence Palladium. I love Palladium!”

~ Jensen Huang, CEO,Nvidia

Tran Nguyen, senior director of design services at Arm, emphasized the importance of scalable validation and verification tools in driving innovation across AI, automotive, and data center applications.

Conclusion:

In the relentless pursuit of technological advancement, Cadence remains at the forefront, driving innovation and empowering design teams to realize their vision. With the unveiling of the Palladium Z3 and Protium X3 platforms, coupled with domain-specific apps and industry collaborations, Cadence reaffirms its position as a trusted partner in the semiconductor ecosystem. The future of chip design is brighter than ever, thanks to Cadence’s Dynamic Duo III.